# Investigation of Microstructural Evolution in **Advanced 3-D Logic and Memory Devices**

Nikita Gaurav, Brenden Hamilton, Matthew Muschar, Ce Ouyang Faculty Advisors: Professor John Blendell & Professor Carol Handwerker **Industrial Sponsors: Peng Su, Juniper Networks**

Three-dimensional logic and memory devices are increasing in popularity due to increases in computational power while minimizing space. However, this change in structure plays into the question of reliability of the solder joints within each layer of the device. This project seeks to explore the effects of various extended use regimes on small 3D solder joints. Intermetallic compound (IMC) growth is measured after thermal aging and the relative damage in the solder joint is assessed to provide a better qualitative and quantitative measure of the joint reliability.

This work is sponsored by Juniper Networks, based in Sunnyvale California.

**Intermetallic Growth of Ni-Sn System**

The nickel layers are used as a

barrier between the tin and

copper. Nickel forms an IMC with

tin significantly slower than with

copper, helping to prevent critical

failure early in the lifetime of the

## **Project Motivation & Goals**

By stacking layers of logic and memory devices in a 3-Dimensional architecture, systems can utilize less space and increase computation via shorter signal pathways. However, it is relatively unknown how this new architecture will affect the reliability of the solder joints, a vital component. Statistically significant data must be obtained to analyze the response of the solder to different stress states. During fabrication, the tin alloy is reflowed to attach each layer; the solder joint on the bottom level has seen 3 more heat cycles than the top level. As the 3D device thermally expands, the solder on the edges will experience a greater displacement and resulting in larger forces applied. Thermal aging can be utilized to assess solder damage.

### Objectives:

- Measure IMC thermal aging

- Analyze damage to solder ball

- Characterize geometric effect to reliability

thermally cycled 500 times

### **Results & Discussion Solder Ball Composition**

**Mechanical Damage of the Solder**

Central Solder

Central Solder

Damage Heat Maps for Sequential Testing Solder Balls from as (a) as received, (b) 250 hours/cycles, and (c) 500

By analyzing the mechanical damage in the solder due to

cracking and necking, the damage can be mapped to the

location of the solder ball. The lowest layers and near the

perimeter appear more susceptible to mechanical damage

over extended use. This is due to additional tin reflows and

increased displacement during thermal cycling.

**Solder Necking Damage**

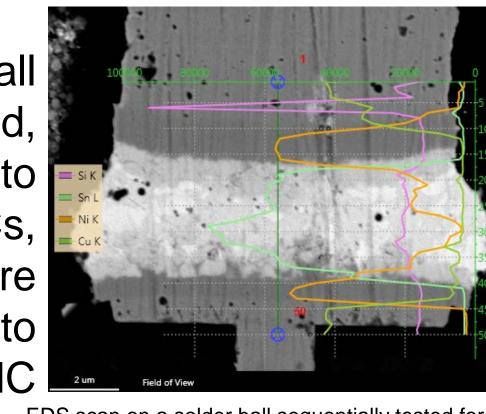

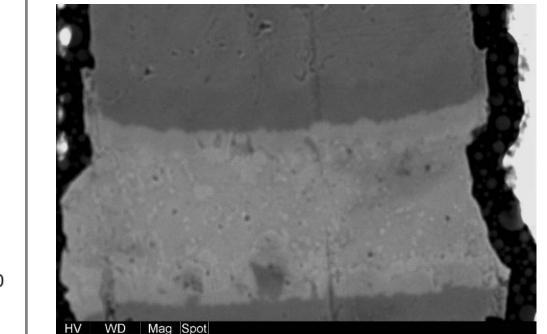

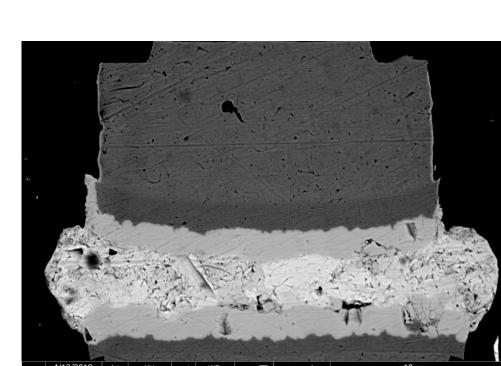

Via EDS scans, the solder ball composition can be confirmed, defining the regions from top to bottom as Cu, Ni, Ni<sub>x</sub>Sn<sub>v</sub> IMCs, tin, Ni<sub>x</sub>Sn<sub>v</sub> IMCs, Ni, and Cu. More precise scans are necessary to the specific determine compositions.

(a) As Received

(b) **SEQ 250**

(c) **SEQ 500**

(a) As Received

Outer Solder

Outer Solder

250 hours/cycles. Solder ball is located on the 3<sup>rd</sup> aver from the bottom on the outer set of TSVs.

Outer Solder

Outer Solder

solder.

$$3.28*rac{2T_{Ni}}{T_{Sn}}\geq 1$$

The coefficient of the inequality stems from the molar mass and density of the Ni and Sn systems

The inequality represents the necessary ratio of thickness for nickel and tin to guarantee excess nickel is present and prevent considerably amounts of copper tin intermetallic within the lifetime of the component.

| Thickness Ni         | Thickness Sn   | Critical Ratio | Minimum CR | Necessary CR |

|----------------------|----------------|----------------|------------|--------------|

| 2.34 <u>+</u> .27 μm | 6.25 + 1.10 μm | 1.84           | 1.38       | 0.75         |

The nickel present is more than double the necessary size to consume the tin. The ratio minimizing boundaries values from the uncertainty still produce a significantly large ratio. Hence, the IMC regions analyzed in this study should be from

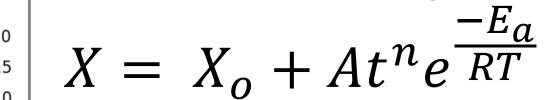

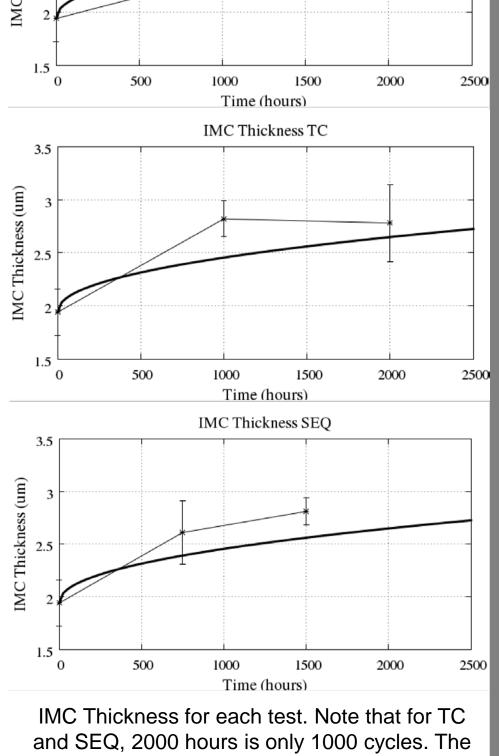

the Ni-Sn system, exclusively. 35 Through the thermal tests, IMC growth was measured an various read points and plotted against a numerical model constant temperature growth 150°C fit from an Arrhenius relationship.

The Ni-Sn system is known to have n value of 0.46 as well as an activation energy of -47.1 kJ/mol. The fitting constant of A was found to have a value of ~19,000. The HTH was expected to have the highest IMC growth

rate, followed by SEQ, due to the largest time spent at high temperature. The difference in expected and actual trends shown can possibly be attributed to the large uncertainty in  $X_0$  value from the as received samples.

# growth relative to

|                                                          |  |                        |                                    |             | 3. 3. C.  |  |  |  |

|----------------------------------------------------------|--|------------------------|------------------------------------|-------------|-----------|--|--|--|

|                                                          |  |                        |                                    |             |           |  |  |  |

|                                                          |  |                        |                                    |             |           |  |  |  |

| . 4                                                      |  |                        | * 1                                | •           |           |  |  |  |

|                                                          |  | <u> </u>               | CARLES TO LA TARREST CO.           | *;          | V. L. & P |  |  |  |

|                                                          |  | - 200 E 100 E          |                                    | - Land      |           |  |  |  |

|                                                          |  |                        |                                    |             |           |  |  |  |

|                                                          |  |                        | <u>L</u>                           |             | ••        |  |  |  |

|                                                          |  |                        | pinet.                             | 200 FM      |           |  |  |  |

|                                                          |  |                        |                                    |             | •         |  |  |  |

|                                                          |  |                        |                                    |             |           |  |  |  |

|                                                          |  |                        |                                    | 27. 1168 p. |           |  |  |  |

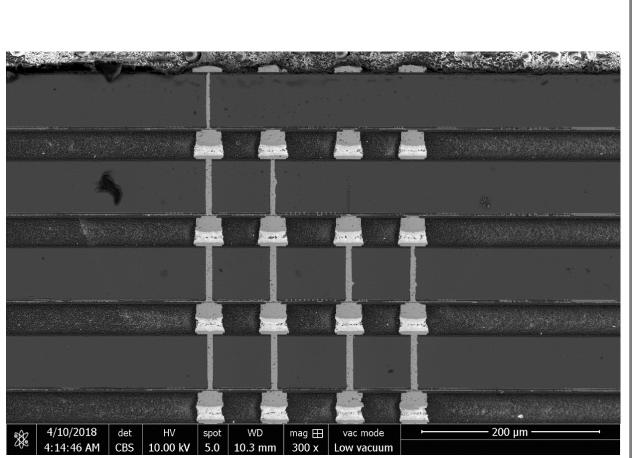

| 4/10/2018 de<br>4:14:46 AM CB                            |  | spot WD<br>5.0 10.3 mm | mag ⊞ vac mode<br>300 x Low vacuum | 200         | μm ————   |  |  |  |

|                                                          |  |                        |                                    |             |           |  |  |  |

| Left-most quadrant of solder balls with TSVs in a sample |  |                        |                                    |             |           |  |  |  |

| thermally evoled 500 times                               |  |                        |                                    |             |           |  |  |  |

# **Experimental Setup &** Procedure

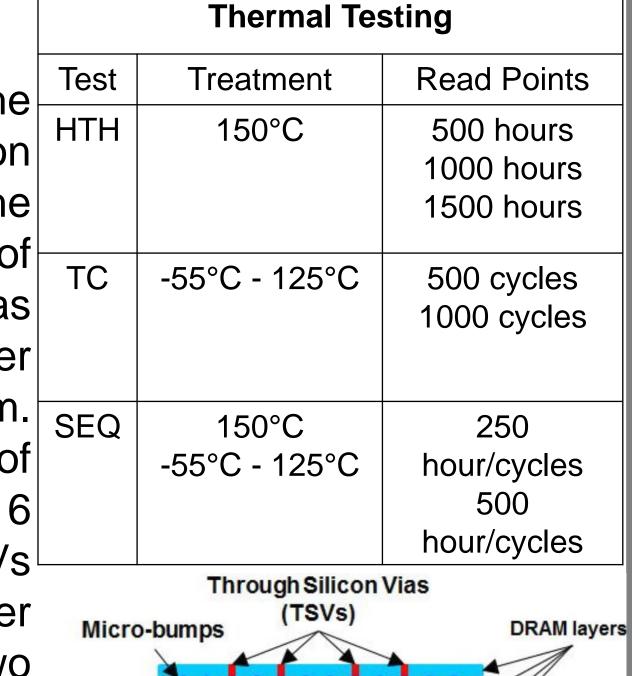

Three tests were used to thermally age 3D memory chips: high temperature hold (HTH), thermal cycling (TC), and a sequential (SEQ) test of HTH and TC.

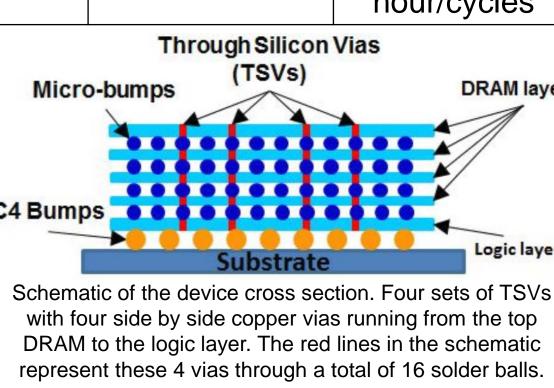

| At each read point, the |   |  |  |  |  |  |  |

|-------------------------|---|--|--|--|--|--|--|

| analysis focused on     |   |  |  |  |  |  |  |

| four sections of the    |   |  |  |  |  |  |  |

| chip, the four sets of  |   |  |  |  |  |  |  |

| Through Silicon Vias    |   |  |  |  |  |  |  |

| (TSVs) and the solder   |   |  |  |  |  |  |  |

| bumps attaching them.   |   |  |  |  |  |  |  |

| The four points of      |   |  |  |  |  |  |  |

| interest consist of 16  |   |  |  |  |  |  |  |

| solder bump/TSVs        |   |  |  |  |  |  |  |

| each, with the outer    |   |  |  |  |  |  |  |

| two and inner two       |   |  |  |  |  |  |  |

| being equivalent due to | _ |  |  |  |  |  |  |

| axisymmetric geometry.  | С |  |  |  |  |  |  |

| At each point, the      |   |  |  |  |  |  |  |

| solder is analyzed for  |   |  |  |  |  |  |  |

|                         |   |  |  |  |  |  |  |

relative damage and IMC growth. Using BSE SEM imaging, the IMC layers can be determined by contrast and their thickness measured. Using the same image, the damage is measured. The damage exists as necking, large single cracks, and regions of numerous small cracks. The damage is defined as the percentage of the width that the cracks/necking extend

□ □ across the solder ball, hence, 100% damage (or a score of 10/10) will have cracks extending the entire width, preventing electronic transport through the solder ball and TSV. Damage, especially cracking, will enable both electrical and mechanical failure of the device. Hence, it is vital to understand the effects of geometry and dimensionality on damage.

# Outer Solder Central Solder Outer Solder (b) TC 500 Outer Solder Central Solder Outer Solder (c) TC 1000

TC 1000. Note the change in color scale to increase image contrast Analysis of the necking of the solder ball shows two distinct trends. The necking seems to increase in lower layers, however, there is very little difference from inner to outer locations. Additionally, only the early cycles appear to influence necking.

Damage maps for thermal cycled samples displaying only the necking. (a) As Received (b) TC 500 (c)

## **Summary & Recommendations**

Through damage analysis, it is shown that damage is more likely on solder balls near the edges of the chips and at the lower layers. This is most likely due to both increased displacement fields and multiple reflows of the solder during fabrication. It is recommended that use conditions similar to the sequential testing be avoided to prevent severe damage to the solder.