May 17, 2016

High-efficiency power amplifier could bring 5G cell phones

|

|

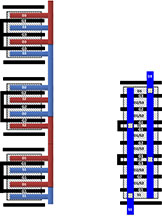

This diagram shows the standard layout of transistors in cell phone power amplifiers, at left, and a new highly efficient amplifier design, at right. The new design could help make possible next-generation cell phones, low-cost collision-avoidance radar for cars and lightweight microsatellites for communications. (Purdue University image) |

WEST LAFAYETTE, Ind. – A new highly efficient power amplifier for electronics could help make possible next-generation cell phones, low-cost collision-avoidance radar for cars and lightweight microsatellites for communications.

Fifth-generation, or 5G, mobile devices expected around 2019 will require improved power amplifiers operating at very high frequencies. The new phones will be designed to download and transmit data and videos faster than today's phones, provide better coverage, consume less power and meet the needs of an emerging "Internet of things" in which everyday objects have network connectivity, allowing them to send and receive data.

Power amplifiers are needed to transmit signals. Because today's cell phone amplifiers are made of gallium arsenide, they cannot be integrated into the phone's silicon-based technology, called complementary metal-oxide-semiconductor (CMOS). The new amplifier design is CMOS-based, meaning it could allow researchers to integrate the power amplifier with the phone's electronic chip, reducing manufacturing costs and power consumption while boosting performance.

"Silicon is much less expensive than gallium arsenide, more reliable and has a longer lifespan, and if you have everything on one chip it's also easier to test and maintain," said Saeed Mohammadi, an associate professor of electrical and computer engineering at Purdue University. "We have developed the highest efficiency CMOS power amplifier in the frequency range needed for 5G cell phones and next-generation radars."

Findings are detailed in two papers, one to be presented during the IEEE International Microwave Symposium on May 24 in San Francisco, authored by former doctoral student Sultan R. Helmi, who has graduated, and Mohammadi. They authored another paper with former doctoral student Jing-Hwa Chen to appear in a future issue of the journal IEEE Transactions on Microwave Theory and Techniques.

The amplifier achieves an efficiency of 40 percent, which is comparable to amplifiers made of gallium arsenide.

The researchers created the new type of amplifier using a high-performance type of CMOS technology called silicon on insulator (SOI). The new amplifier design has several silicon transistors stacked together and reduces the number of metal interconnections normally needed between transistors, reducing "parasitic capacitance," which hinders performance and can lead to damage to electronic circuits.

"We have merged transistors so we are using less metallization around the device, and that way we have reduced the capacitance and can achieve higher efficiencies," Mohammadi said. "We are trying to eliminate metallization between transistors."

The new amplifiers could bring low-cost collision-avoidance radars for cars and electronics for lightweight communications microsatellites.

The CMOS amplifiers could allow researchers to design microsatellites that are one-hundredth the weight of today's technology.

Three U.S. patents related to the amplifier have been issued. The research was funded partially by the U.S. Defense Advanced Research Projects Agency.

The researchers are working on a new version of the amplifier that is twice as powerful. Further work will be needed to integrate the amplifier into a cell phone chip.

Writer: Emil Venere, 765-494-4709, venere@purdue.edu

Source: Saeed Mohammadi, saeedm@purdue.edu

Note to Journalists: A copy of the research papers is available from Emil Venere at Purdue, 765-494-4709, venere@purdue.edu

ABSTRACT

A Highly Efficient mm-Wave CMOS SOI Power Amplifier

Sultan R. Helmi, and Saeed Mohammadi Purdue University, West Lafayette, IN, 47907, USA 1

Three mm-wave power amplifiers (PAs), each with 6 stacked transistors, are implemented in GlobalFoundries 45 nm CMOS SOI technology. As experimentally demonstrated, the design with two triple-Cascode cells with combined transistor layouts achieves the best power performance among the three designs. It achieves a power-added efficiency (PAE) of higher than 40% at 46 GHz and a relatively good power performance from 42 to 54 GHz. At 46 GHz the PA, biased under 6 V, measures a saturated output power (PSAT) of 22.4 dBm, a linear gain of 17.4 dB, a peak PAE of 42%, and a drain efficiency (DE) of 49%. Under a smaller supply voltage of 4.8 V, PSAT is reduced to 20 dBm while DE and peak PAE increase to 53% and 45%, respectively.

ABSTRACT

High-Efficiency Microwave and MM-Wave Stacked Cell CMOS SOI Power Amplifiers

Sultan R. Helmi, Student Member, IEEE, Jing-Hwa Chen, Student Member, IEEE, and Saeed Mohammadi, Senior Member, IEEE

Design and implementation of high efficiency microwave and mm-wave CMOS SOI power amplifiers (PAs) based on stacked cell approach is presented. A triple Cascode cell (CS-CG-CG, CS: Common-Source, CG: Common-Gate) as building block of the stacked cell PA facilitates high gain, high power, high efficiency and compact design. Two stacked cell PAs have been implemented in a standard 45 nm CMOS Silicon on Insulator (SOI) technology. The first PA operating at K-Band (24 to 28 GHz) is designed with three stacked triple Cascode cells. Each cell uses three standard transistors with separate layout. At 24 GHz, the K-Band PA biased under a supply voltage of 10.8 V measures a maximum linear power gain of 13 dB, a saturated output power PSAT of 25.3 dBm, a -1 dB output power P1dB of 23.8 dBm and a peak power-added efficiency PAE of 20%. The second PA targeted at U-Band frequencies is designed with two stacked triple Cascode cells. Transistors (CS-CG-CG) in this design have a combined layout to mitigate internodal parasitic capacitances, leading to significant improvement in the PAE at mm-wave frequencies. The U-Band PA achieves a relatively good power performance from 42 to 54 GHz. At 46 GHz, the PA, biased under a supply voltage of 6 V, measures a saturated output power (PSAT) of 22.4 dBm, a linear gain of 17.4 dB, and an unprecedented peak PAE of 42%.