February 7, 2019

New center to bring higher-performance computing at lower cost

Researchers will investigate how to boost computing and maintain lower manufacturing costs through integrating multiple chips into a single assembled unit. (Purdue University stock photo)

Download image

Researchers will investigate how to boost computing and maintain lower manufacturing costs through integrating multiple chips into a single assembled unit. (Purdue University stock photo)

Download image

WEST LAFAYETTE, Ind. — The cost of computing has been steadily decreasing as companies pack more components and functions onto a single chip, for applications ranging from smartphones to large mainframe computers.

The problem is that there is a limit to how small the main components that make these functions possible; transistors, can shrink to fit on-chip and still provide higher performance and energy efficiency.

Instead of cramming more transistors onto a single chip, companies have been exploring stacking or arranging multiple chips close to each other into a single assembled unit to boost performance and keep manufacturing costs low – a technique called heterogeneous integration.

Through a new center funded by the Semiconductor Research Corporation (SRC), Purdue University and Binghamton University will improve how to "package," or protect and supply power to, chips of various functions integrated together.

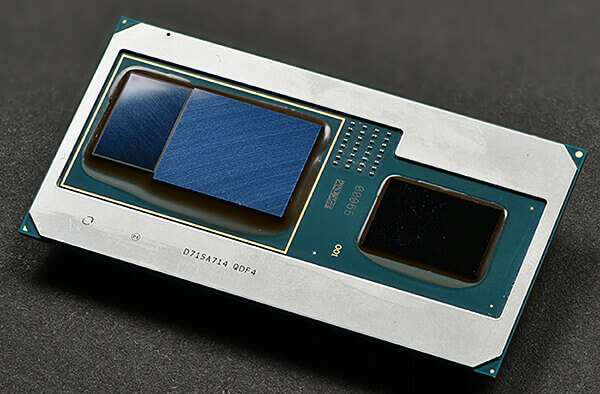

Corporations have started integrating chips of various functions into a platform rather than packing more functions onto the same chip. A new center will research ways to integrate and power these systems for better performance and energy efficiency. (Intel photo/Walden Kirsch)

Download image

Corporations have started integrating chips of various functions into a platform rather than packing more functions onto the same chip. A new center will research ways to integrate and power these systems for better performance and energy efficiency. (Intel photo/Walden Kirsch)

Download image

The Center for Heterogeneous Integration Research in Packaging, or CHIRP, will be co-directed by Ganesh Subbarayan, professor of mechanical engineering at Purdue, and Bahgat Sammakia, vice president for research and a distinguished professor of mechanical engineering at Binghamton. Subbarayan developed the winning proposal together with Sammakia and Kanad Ghose, professor of computer science at Binghamton.

Founding members of SRC's CHIRP – including ARM, IBM, Intel, NXP Semiconductors, Samsung and Texas Instruments – will guide the research at Purdue and Binghamton.

Transistors contain gates that switch electrical current on and off to form a string of 0s and 1s, instructing computers to perform a certain function. Billions of transistors make up today's processors and memory chips.

The prediction that the number of transistors in an integrated circuit doubles about every two years – an observation called Moore's law – has held steady for the past 50 years. Doubling that number means that transistors have shrunk to fit onto computer chips.

"That trend cannot continue without some significant changes in thinking; integrating more transistors by area reduction is increasingly a very expensive proposition," Subbarayan said. "With heterogeneous integration, we can achieve improved performance at low cost by integrating more chips on a package instead of achieving the same with a single chip."

As chips are integrated on a package, there's a need to efficiently provide power to the chips, ensure mechanical integrity and remove heat from the package. CHIRP will be addressing these challenges with novel materials and better package design.

“Anywhere you have chips that benefit from small transistors, we’re heading toward heterogeneous integration,” Sammakia said. “It’s really the only solution available for the next five to 10 years. Other approaches, like quantum computing, are at least a decade away.”

SRC, a world-class technology research consortium, promotes collaborations among academic institutions, technology companies and government agencies. It will provide $2.1 million to the center in the first four years. Another $2.1 million will come from the campuses, the State University of New York and other sources.

"The Purdue-Binghamton team has a successful track record of working with the semiconductor industry," said Kwok Ng, senior director at SRC. "CHIRP will capitalize on this heritage and partner with SRC to address industry needs."

Roughly a dozen faculty members in engineering and computer science at the two institutions will participate in the center’s research. The center is expected to expand in faculty participation as SRC initiates additional projects in future years.

Writer: Kayla Wiles, 765-494-2432, wiles5@purdue.edu

Source: Ganesh Subbarayan, 765-494-9770, ganeshs@purdue.edu