Rare chance for extended chip design experience

WEST LAFAYETTE, Ind. — Zach Ellis was a senior electrical and computer engineering major at Purdue University with an interest in chip design when he was introduced to the SCALE program (Scalable Asymmetric Lifecycle Engagement). The defense sector semiconductor workforce development program, led by Purdue, funded by the Department of Defense, and managed by NSWC Crane, provided a rare opportunity to learn more about the research pipeline for chip design that has helped shape his career trajectory.

“There aren’t a lot of easy opportunities for students, or anyone who’s not directly involved in research or industry, to get familiar with chip design or the semiconductor industry,” said Ellis. “I think having this introduction made me realize that I’m very interested in doing research, and what that looks like, and what to expect. The opportunity has been important for me, especially as I pursue graduate degrees.”

Ellis graduated with the Purdue Class of 2022, recently completed a summer internship at Texas Instruments, and recently began a graduate program at Georgia Tech — one of the 17 SCALE member institutions. Although his interest in graduate work predates his involvement with SCALE, the program sharpened the focus of his graduate studies.

In his sophomore year at Purdue, Ellis took an introductory chip design course — Purdue’s Application of Specific Integrated Circuits (ASIC) Design Laboratory. The course whetted his interest in chip design; and in subsequent semesters he served as a teaching assistant for the course, taught by Mark Johnson, a senior lecturer of electrical and computer engineering.

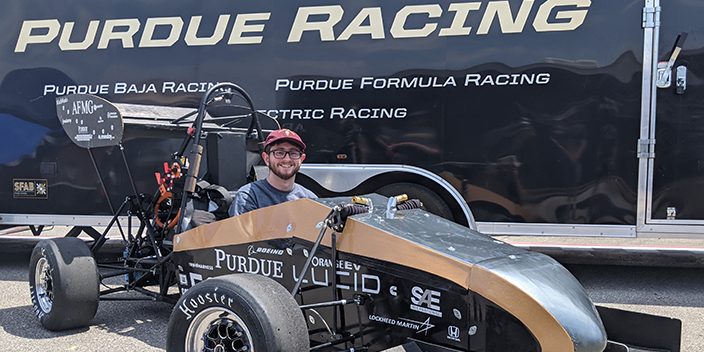

In the summer between his junior and senior years, as part of his involvement with the Purdue Electric Racing team, Ellis designed a chip for a communication protocol commonly used in the automotive industry. He submitted the design for an open-source controller area network (CAN) controller to a competitive program run by Google and SkyWater Technology. The program produces winning designs and Ellis’ design was selected for production, an honor that came to the attention of the ASIC Design Lab professor. Johnson encouraged Ellis to become more involved in the research landscape at Purdue, which led him to SCALE.

SCALE funded Ellis’ research, which allowed him to give up his position as a teaching assistant, and widened his horizons.

“SCALE gave me the opportunity to engage in some more advanced research in my topic of choice. Through that I was able to meet a lot of cool professors and students and get more involved with research at Purdue,” Ellis said.

The program also offered access to sophisticated and costly tools and resources for learning chip design that are not otherwise readily available, Ellis said. For example, the ASIC design course he helped to teach offers exceptional software and simulation tools that are only available to students, and producing a design can cost in the tens of thousands of dollars. Contrast that with coding, where free online coding tools abound and a printed circuit board costs $5.

“If students are interested in chip design, there’s not a lot of easy opportunities to get familiarized with chip design or the semiconductor industry. SCALE offered that access,” Ellis said.

Led by Purdue and funded by the Department of Defense, SCALE facilitates a unique and ambitious approach to training highly skilled U.S. microelectronics engineers, hardware designers and manufacturing experts. SCALE brings together a public-private-academic partnership of 17 universities and 34 partners within the defense industry and government. The industry and government partners regularly meet and update a list of knowledge, skills, and abilities important for new entrants to the workforce. The SCALE universities then update their curriculum to ensure the students are prepared for upcoming needs in the rapidly advancing microelectronics field.

Writer: Mary Martialay, mmartial@purdue.edu

Source:Zach Ellis